Плата ввода 1x100G,1x40G SKаTCA-100/40

Описание:

Новая коммуникационная плата ввода SKаTCA-100_40 выпущенная в 2017 году, предназначена прежде всего для телекоммуникационных приложений и работы в системах сетевой безопасности. Также она может использоваться в качестве платформы для IMS-серверов, медиашлюзов, серверов управления трафиком, контроллеров беспроводных точек доступа и т.д. Плата позволяет осуществлять подключение к сетям 100Гбит, 40Гбит, 10Гбит с использованием современных оптических модулей, QSFP28, QSFP.

Новая коммуникационная плата ввода SKаTCA-100_40 выпущенная в 2017 году, предназначена прежде всего для телекоммуникационных приложений и работы в системах сетевой безопасности. Также она может использоваться в качестве платформы для IMS-серверов, медиашлюзов, серверов управления трафиком, контроллеров беспроводных точек доступа и т.д. Плата позволяет осуществлять подключение к сетям 100Гбит, 40Гбит, 10Гбит с использованием современных оптических модулей, QSFP28, QSFP.

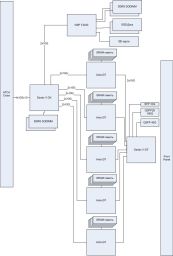

Она отвечает спецификациям PICMG 3.0 и PICMG 3.1 Ethernet Over PICMG и выполнена на базе процессора NXP(бывший Freescale) QorIQ T4240 второго поколения с поддержкой 24 вычислительных ядер, микросхемы программируемой логики ПЛИС Intel StratixV GX, микросхемы программируемой логики ПЛИС Intel StratixV GT и пяти микросхемах программируемой логики ПЛИС Intel ArriaV.

ПЛИС Intel StratixV GT предназначена для подключение к сетям 100Гбит, 40Гбит, 10Гбит, обработки потоков данных, реализации алгоритмов DPI, реализации алгоритмов балансировки.

ПЛИС Intel StratixV GX имеет следующие связи: два линка 10Гбит/c с каждой ПЛИС ArriaV. 4 28 Гбит линка с модулем QSFP28, 4 10 Гбит линка с модулем QSFP, один линк 10Гбит/c с моделм SFP+.

ПЛИС Intel StratixV GX предназначена для организации матрицы коммутации между процессорами, другими платами фрейма Advanced TCA. Также ПЛИС может выполнять функции предварительного анализа и обработки потоков данных, реализации алгоритмов DPI.

ПЛИС Intel StratixV GX имеет следующие связи: два линка 10Гбит/c процессором, 4 линка 10Гбит/c с каждым слотов фрейма AdvancedTCA (максимум 14 слотов Full Mesh), два линка 10Гбит/c с каждой ПЛИС ArriaV.

ПЛИС ArriaV предназначены для реализации алгоритмов DPI, фильтрации, поиска сигнатур и т.д. Для хранения различных таблиц, используемых в алгоритмах на каждую ПЛИС подключено 5 микросхем памяти с быстрым случайным доступом.

Характеристики:

- Процессора 24-Core NXP QorIQ T4240®

- Power Architecture e6500 — 64-битное много поточное ядро с технологией AltiVec с ча- стотой до 1,8 ГГц

- физических ядер 12

- L2 кэш 6 Мбайт

- CoreNet Platform Cache 1.5MB

- Встроенные аппаратные ускорители:

- Data Path Acceleration Architecture (DPAA) первого и второго поколений;

- Data Compression Engine (DCE);

- QUICC Engine

- Pattern Matching Engine (PME2.0) to 10Gb/s

- Загрузка ОС SD карта

- Хранилище - 2 диска SSD

- Память DDR3 1800 до 16 ГБ

- ПЛИС Intel StratixV GX:

- 490000 логических элементов

- 66 трансиверов 14.1 Гбит/сек

- 41 Мбит встроенной памяти

- ПЛИС Intel StratixV GT

- 425000 логических элементов

- 32 трансивера 14.1 Гбит/сек

- 4 трансивера 28.05 Гбит/сек

- 50 Мбит встроенной памяти

- ПЛИС Intel Arria V GT:

- 362 000 логических элементов

- 6 трансиверов 14.1 Гбит/сек

- 20 Мбит встроенной памяти

- Механические характеристики:

- Форм фактор –PICMG Advanced TCA

- Программное обеспечение:

- U-Boot Universal Boot Loader

- Linux

- Библиотеки и программы T4240 для решения задач обработки сетевого трафика.

- IP ядра для ПЛИС StratixV, реализующие функции матрицы коммутации, DPI анализа и т.д.

- IP ядра для ПЛИС Arria V, реализующие функции приема и анализа данных сетей Ethernet, SDH/Sonet и т.д

Области применения:

- Построение сетевой инфраструктуры

- Системы сетевой безопасности

- Обработка изображений

- Организация хранилищ данных

- Облачные вычисления

- Реализация алгоритмов с минимальной задержкой в финансовом секторе

- Реализация систем машинного обучения